Design of generalized search interfaces for health informatics

Contents

| Computer memory and data storage types |

|---|

| Volatile |

| Non-volatile |

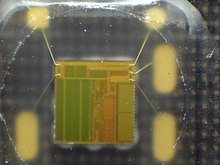

Upper insulator: ONO

Lower insulator: tunnel oxide

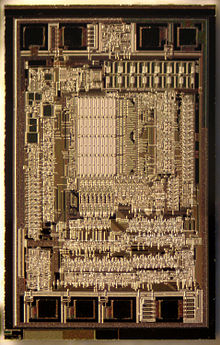

EEPROM or E2PROM (electrically erasable programmable read-only memory) is a type of non-volatile memory. It is used in computers, usually integrated in microcontrollers such as smart cards and remote keyless systems, or as a separate chip device, to store relatively small amounts of data by allowing individual bytes to be erased and reprogrammed.

EEPROMs are organized as arrays of floating-gate transistors. EEPROMs can be programmed and erased in-circuit, by applying special programming signals. Originally, EEPROMs were limited to single-byte operations, which made them slower, but modern EEPROMs allow multi-byte page operations. An EEPROM has a limited life for erasing and reprogramming, reaching a million operations in modern EEPROMs. In an EEPROM that is frequently reprogrammed, the life of the EEPROM is an important design consideration.

Flash memory is a type of EEPROM designed for high speed and high density, at the expense of large erase blocks (typically 512 bytes or larger) and limited number of write cycles (often 10,000). There is no clear boundary dividing the two, but the term "EEPROM" is generally used to describe non-volatile memory with small erase blocks (as small as one byte) and a long lifetime (typically 1,000,000 cycles). Many past microcontrollers included both (flash memory for the firmware and a small EEPROM for parameters), though the trend with modern microcontrollers is to emulate EEPROM using flash.

As of 2020, flash memory costs much less than byte-programmable EEPROM and is the dominant memory type wherever a system requires a significant amount of non-volatile solid-state storage. EEPROMs, however, are still used on applications that only require small amounts of storage, like in serial presence detect.[1][2]

History

Early attempts

In the early 1970s, some studies, inventions, and development for electrically re-programmable non-volatile memories were performed by various companies and organizations.

In 1971, early research was presented at the 3rd Conference on Solid State Devices, Tokyo in Japan by Yasuo Tarui, Yutaka Hayashi, and Kiyoko Nagai at Electrotechnical Laboratory; a Japanese national research institute.[3] They fabricated an electrically re-programmable non-volatile memory in 1972,[4][5][6] and continued this study for more than 10 years.[7] However this early memory depended on capacitors to work,[4] which modern EEPROM lacks.

In 1972 IBM patented an electrically re-programmable non-volatile memory invention.[8] Later that year, an avalanche injection type MOS was patented by Fujio Masuoka, the inventor of flash memory, at Toshiba[9] and IBM patented another later that year.[10]

In 1974, NEC patented a electrically erasable carrier injection device.[11] The next year, NEC applied for the trademark "EEPROM®" with the Japan Patent Office. The trademark was granted in 1978.[12][13]

The theoretical basis of these devices is avalanche hot-carrier injection. In general, programmable memories, including EPROM, of early 1970s had reliability and endurance problems such as the data retention periods and the number of erase/write cycles.[14]

Most of the major semiconductor manufactures, such as Toshiba,[9][5] Sanyo (later, ON Semiconductor),[15] IBM,[16] Intel,[17][18] NEC (later, Renesas Electronics),[19] Philips (later, NXP Semiconductors),[20] Siemens (later, Infineon Technologies),[21] Honeywell (later, Atmel),[22] Texas Instruments,[23] studied, invented, and manufactured some electrically re-programmable non-volatile devices until 1977.

Modern EEPROM

The first EEPROM that Fowler-Nordheim tunnelling to erase data was invented by Bernward and patented by Siemens in 1974.[24] In February 1977, Israeli-American Eliyahou Harari at Hughes Aircraft Company patented in the US a modern EEPROM technology, based on Fowler-Nordheim tunnelling through a thin silicon dioxide layer between the floating-gate and the wafer. Hughes went on to produce this new EEPROM devices.[25]

In May 1977, some important research result was disclosed by Fairchild and Siemens. They used SONOS (polysilicon-oxynitride-nitride-oxide-silicon) structure with thickness of silicon dioxide less than 30 Å, and SIMOS (stacked-gate injection MOS) structure, respectively, for using Fowler-Nordheim tunnelling hot-carrier injection.[26][27]

Around 1976 to 1978, Intel's team, including George Perlegos, made some inventions to improve this tunneling E2PROM technology.[28][29] In 1978, they developed a 16K (2K word × 8) bit Intel 2816 chip with a thin silicon dioxide layer, which was less than 200 Å.[30] In 1980, this structure was publicly introduced as FLOTOX; floating gate tunnel oxide.[31] The FLOTOX structure improved reliability of erase/write cycles per byte up to 10,000 times.[32] But this device required additional 20–22V VPP bias voltage supply for byte erase, except for 5V read operations.[33]: 5–86 In 1981, Perlegos and 2 other members left Intel to form Seeq Technology,[34] which used on-device charge pumps to supply the high voltages necessary for programming E2PROMs. In 1984, Perlogos left Seeq Technology to found Atmel, then Seeq Technology was acquired by Atmel.[35][36]

Electrically alterable read-only memory (EAROM) is a type of EEPROM that can be modified one or a few bits at a time.[37] Writing is a very slow process and again needs higher voltage (usually around 12 V) than is used for read access. EAROMs are intended for applications that require infrequent and only partial rewriting.

Theoretical basis of FLOTOX structure

As is described in former section, old EEPROMs are based on avalanche breakdown-based hot-carrier injection with high reverse breakdown voltage. But FLOTOX theoretical basis is Fowler–Nordheim tunneling hot-carrier injection through a thin silicon dioxide layer between the floating gate and the wafer. In other words, it uses a tunnel junction.[38]

Theoretical basis of the physical phenomenon itself is the same as today's flash memory. But each FLOTOX structure is in conjunction with another read-control transistor because the floating gate itself is just programming and erasing one data bit.[39]

Intel's FLOTOX device structure improved EEPROM reliability, in other words, the endurance of the write and erase cycles, and the data retention period. A material of study for single-event effect about FLOTOX is available.[40]

Today, an academic explanation of the FLOTOX device structure can be found in several sources.[41][42][43]

Today's EEPROM structure

Nowadays, EEPROM is used for embedded microcontrollers as well as standard EEPROM products. EEPROM still requires a 2-transistor structure per bit to erase a dedicated byte in the memory, while flash memory has 1 transistor per bit to erase a region of the memory.[44]

Security protections

Because EEPROM technology is used for some security gadgets, such as credit cards, SIM cards, key-less entry, etc., some devices have security protection mechanisms, such as copy-protection.[44][45]

Electrical interface

EEPROM devices use a serial or parallel interface for data input/output.

Serial bus devices

The common serial interfaces are SPI, I²C, Microwire, UNI/O, and 1-Wire. These use from 1 to 4 device pins and allow devices to use packages with 8 pins or less.

A typical EEPROM serial protocol consists of three phases: OP-code phase, address phase and data phase. The OP-code is usually the first 8 bits input to the serial input pin of the EEPROM device (or with most I²C devices, is implicit); followed by 8 to 24 bits of addressing, depending on the depth of the device, then the read or write data.

Each EEPROM device typically has its own set of OP-code instructions mapped to different functions. Common operations on SPI EEPROM devices are:

- Write enable (WRENAL)

- Write disable (WRDI)

- Read status register (RDSR)

- Write status register (WRSR)

- Read data (READ)

- Write data (WRITE)

Other operations supported by some EEPROM devices are:

- Program

- Sector erase

- Chip erase commands

Parallel bus devices

Parallel EEPROM devices typically have an 8-bit data bus and an address bus wide enough to cover the complete memory. Most devices have chip select and write protect pins. Some microcontrollers also have integrated parallel EEPROM.

Operation of a parallel EEPROM is simple and fast when compared to serial EEPROM, but these devices are larger due to the higher pin count (28 pins or more) and have been decreasing in popularity in favor of serial EEPROM or flash.

Other devices

EEPROM memory is used to enable features in other types of products that are not strictly memory products. Products such as real-time clocks, digital potentiometers, digital temperature sensors, among others, may have small amounts of EEPROM to store calibration information or other data that needs to be available in the event of power loss. It was also used on video game cartridges to save game progress and configurations, before the usage of external and internal flash memories.

Failure modes

There are two limitations of stored information: endurance and data retention.

During rewrites, the gate oxide in the floating-gate transistors gradually accumulates trapped electrons. The electric field of the trapped electrons adds to the electrons in the floating gate, lowering the window between threshold voltages for zeros vs ones. After sufficient number of rewrite cycles, the difference becomes too small to be recognizable, the cell is stuck in programmed state, and endurance failure occurs. The manufacturers usually specify the maximum number of rewrites being 1 million or more.[46]

During storage, the electrons injected into the floating gate may drift through the insulator, especially at increased temperature, and cause charge loss, reverting the cell into erased state. The manufacturers usually guarantee data retention of 10 years or more.[47]

Related types

Flash memory is a later form of EEPROM. In the industry, there is a convention to reserve the term EEPROM to byte-wise erasable memories compared to block-wise erasable flash memories. EEPROM occupies more die area than flash memory for the same capacity, because each cell usually needs a read, a write, and an erase transistor, while flash memory erase circuits are shared by large blocks of cells (often 512×8).

Newer non-volatile memory technologies such as FeRAM and MRAM are slowly replacing EEPROMs in some applications, but are expected to remain a small fraction of the EEPROM market for the foreseeable future.

Comparison with EPROM and EEPROM/flash

The difference between EPROM and EEPROM lies in the way that the memory programs and erases. EEPROM can be programmed and erased electrically using field electron emission (more commonly known in the industry as "Fowler–Nordheim tunneling").

EPROMs can't be erased electrically and are programmed by hot-carrier injection onto the floating gate. Erase is by an ultraviolet light source, although in practice many EPROMs are encapsulated in plastic that is opaque to UV light, making them "one-time programmable".

Most NOR flash memory is a hybrid style—programming is through hot-carrier injection and erase is through Fowler–Nordheim tunneling.

| Type | Inject electrons onto gate (mostly interpreted as bit=0) |

Duration | Remove electrons from gate (mostly interpreted as bit=1) |

Duration/mode |

|---|---|---|---|---|

| EEPROM | field electron emission | 0.1—5 ms, bytewise | field electron emission | 0.1—5 ms, blockwise |

| NOR flash memory | hot-carrier injection | 0.01—1 ms | field electron emission | 0.01—1 ms, blockwise |

| EPROM | hot-carrier injection | 3—50 ms, bytewise | UV light | 5—30 minutes, whole chip |

See also

- Avalanche breakdown

- DataFlash

- EPROM

- Field electron emission § Fowler–Nordheim tunneling

- Flash memory

- Floating-gate MOSFET

- Intel HEX – file format

- Programmer (hardware)

- Quantum tunnelling

- SREC – file format

- Tunnel junction

- Read-mostly memory (RMM)

References

- ^ "TN-04-42: Memory Module Serial Presence-Detect" (PDF). Micron Technology. 2002. Archived from the original (PDF) on 2022-07-26. Retrieved 2020-10-11.

- ^ "serial presence detect (SPD)". TechTarget. July 2015.

- ^ Tarui, Yasuo; Hayashi, Yutaka; Nagai, Kiyoko (1971-09-01). "Proposal of electrically reprogrammable non-volatile semiconductor memory". Proceedings of the 3rd Conference on Solid State Devices, Tokyo. The Japan Society of Applied Physics: 155–162.

- ^ a b Tarui, Y.; Hayashi, Y.; Nagai, K. (1972). "Electrically reprogrammable nonvolatile semiconductor memory". IEEE Journal of Solid-State Circuits. 7 (5): 369–375. Bibcode:1972IJSSC...7..369T. doi:10.1109/JSSC.1972.1052895. ISSN 0018-9200.

- ^ a b Iizuka, H.; Masuoka, F.; Sato, Tai; Ishikawa, M. (1976). "Electrically alterable avalanche-injection-type MOS READ-ONLY memory with stacked-gate structure". IEEE Transactions on Electron Devices. 23 (4): 379–387. Bibcode:1976ITED...23..379I. doi:10.1109/T-ED.1976.18415. ISSN 0018-9383. S2CID 30491074.

- ^ Rossler, B. (1977). "Electrically erasable and reprogrammable read-only memory using the n-channel SIMOS one-transistor cell". IEEE Transactions on Electron Devices. 24 (5): 606–610. Bibcode:1977ITED...24..606R. doi:10.1109/T-ED.1977.18788. ISSN 0018-9383. S2CID 33203267.

- ^ Tarui, Yasuo; Nagai, Kiyoko; Hayashi, Yutaka (1974-07-19). "Nonvolatile Semiconductor Memory" (PDF). Oyo Buturi. 43 (10): 990–1002. doi:10.11470/oubutsu1932.43.990. ISSN 2188-2290. Archived (PDF) from the original on 2018-03-12.

- ^ US3865652A, Agusta, Benjamin; Chang, Joseph J. & Joshi, Madhukar L., "Method of forming self-aligned field effect transistor and charge-coupled device", issued 1975-02-11

- ^ a b

Masuoka, Fujio (31 August 1972). "Avalanche injection type mos memory".

{{cite journal}}: Cite journal requires|journal=(help) - ^ US3797000A, Agusta, B. & Chang, J., "Non-volatile semiconductor storage device utilizing avalanche injection and extraction of stored information", issued 1974-03-12

- ^ US4016588A, Ohya, Shuichi & Kikuchi, Masanori, "Non-volatile semiconductor memory device", issued 1977-04-05

- ^ "EEPROM". TMview. Archived from the original on 2018-03-10.

- ^ "Reg. No.1342184 – LIVE – REGISTRATION – Issued and Active".

- ^ Moskowitz, Sanford L. (2016). "reliability%20problems"+EPROM+1970s&pg=PA187 Advanced Materials Innovation: Managing Global Technology in the 21st century. John Wiley & Sons. ISBN 9781118986097.

- ^

Rai, Yasuki; Sasami, Terutoshi; Hasegawa, Yuzuru; Okazoe, Masaru (1973-05-18). "Electrically reprogrammable nonvolatile floating gate semi-conductor memory device and method of operation". Archived from the original on 2018-05-03.

{{cite journal}}: Cite journal requires|journal=(help) - ^ Abbas, Shakir A.; Barile, Conrad A.; Lane, Ralph D.; Liu., Peter T (1973-03-16). "US3836992A; Electrically erasable floating gate fet memory cell". pdfpiw.uspto.gov. United States Patent and Trademark Office. Archived from the original on 2018-03-09.

- ^

Frohman, Bentchkowsky D (19 October 1973). "Electrically alterable floating gate device and method for altering same".

{{cite journal}}: Cite journal requires|journal=(help) - ^

Chou, Sunlin (26 February 1973). "Erasable floating gate device".

{{cite journal}}: Cite journal requires|journal=(help) - ^

Ohya, Shuichi; Kikuchi, Masanori (1974-12-27). "Non-volatile semiconductor memory device".

{{cite journal}}: Cite journal requires|journal=(help) - ^ Verwey, J. F.; Kramer, R. P. (1974). "Atmos—An electrically reprogrammable read-only memory device". IEEE Transactions on Electron Devices. 21 (10): 631–636. Bibcode:1974ITED...21..631V. doi:10.1109/T-ED.1974.17981. ISSN 0018-9383.

- ^ B., Roessler; R. G., Mueller (1975). "Erasable and electrically reprogrammable read-only memory using the N-channel SIMOS one-transistor cell". Siemens Forschungs und Entwicklungsberichte. 4 (6): 345–351. Bibcode:1975SiFoE...4..345R.

- ^

Jack, S; Huang, T. (8 September 1975). "Semiconductor memory cell".

{{cite journal}}: Cite journal requires|journal=(help) - ^ Gosney, W. M. (1977). "DIFMOS—A floating-gate electrically erasable nonvolatile semiconductor memory technology". IEEE Transactions on Electron Devices. 24 (5): 594–599. Bibcode:1977ITED...24..594G. doi:10.1109/T-ED.1977.18786. ISSN 0018-9383. S2CID 45636024.

- ^ GB1517925A, "Storage field effect transistors", issued 1978-07-19

- ^ "1027459330501acc.pdf" (PDF). Archived (PDF) from the original on 2015-02-07. Retrieved 2015-02-05.

- ^ Chen, P. C. Y. (May 1977). "Threshold-alterable Si-gate MOS devices". IEEE Transactions on Electron Devices. 24 (5): 584–586. Bibcode:1977ITED...24..584C. doi:10.1109/T-ED.1977.18783. ISSN 0018-9383. S2CID 25586393.

- ^ Rossler, B. (May 1977). "Electrically erasable and reprogrammable read-only memory using the n-channel SIMOS one-transistor cell". IEEE Transactions on Electron Devices. 24 (5): 606–610. Bibcode:1977ITED...24..606R. doi:10.1109/T-ED.1977.18788. ISSN 0018-9383. S2CID 33203267.

- ^ Simko, Richard T. (17 March 1977). "Electrically programmable and electrically erasable MOS memory cell".

- ^ Frohman-Bentchkowsky, Dov; Mar, Jerry; Perlegos, George; Johnson, William S. (15 December 1978). "Electrically programmable and erasable MOS floating gate memory device employing tunneling and method of fabricating same".

- ^ Dummer, G. W. A. (2013). Electronic Inventions and Discoveries: Electronics from Its Earliest Beginnings to the Present Day. Elsevier. ISBN 9781483145211.

- ^ Johnson, W.; Perlegos, G.; Renninger, A.; Kuhn, G.; Ranganath, T. (1980). "A 16Kb electrically erasable nonvolatile memory". 1980 IEEE International Solid-State Circuits Conference. Digest of Technical Papers. Vol. XXIII. pp. 152–153. doi:10.1109/ISSCC.1980.1156030. S2CID 44313709.

- ^

Euzent, B.; Boruta, N.; Lee, J.; Jenq, C. (1981). "Reliability Aspects of a Floating Gate E2 PROM". 19th International Reliability Physics Symposium. pp. 11–16. doi:10.1109/IRPS.1981.362965. S2CID 41116025.

The Intel 2816 uses the FLOTOX structure, which has been discussed in detail in the literaturel. Basically, it uses an oxide of less than 200A thick between the floating polysilicon gate and the N+ region as shown in Figure 1.

- ^ 2816A-2 PDF Datasheet - Intel Corporation - Datasheets360.com. Intel. October 1983.

- ^ "Seeq Technology » AntiqueTech". Archived from the original on 2014-10-02.

- ^ Rostky, George (July 2, 2002). "Remembering the PROM knights of Intel". EE Times. Archived from the original on September 29, 2007. Retrieved 2007-02-08.

- ^ Atmel AT28C16 datasheet (PDF) (0540B ed.). October 1998. Archived (PDF) from the original on 2017-08-29.

- ^ Ciarcia, Steve (1981). Ciarcia's Circuit Cellar. Circuit Cellar. ISBN 978-0-07-010963-6.

- ^ Gutmann, Peter (2001-08-15). "Data Remanence in Semiconductor Devices". 10th USENIX SECURITY SYMPOSIUM. IBM T. J. Watson Research Center: 39–54. Archived from the original on 2016-10-12.

- ^ Janwadkar, Sudhanshu (2017-10-24). "Fabrication of Floating Gate MOS (FLOTOX)". www.slideshare.net.

- ^ Koga, R.; Tran, V.; George, J.; Crawford, K.; Crain, S.; Zakrzewski, M.; Yu, P. "SEE Sensitivities of Selected Advanced Flash and First-In-First-Out Memories" (PDF). The Aerospace Corporation. Archived (PDF) from the original on 2018-03-14.

- ^ Fuller, Dr. Lynn (2012-02-22). CMOS Process Variations EEPROM Fabrication Technology. Microelectronic Engineering, Rochester Institute of Technology.[permanent dead link]

- ^ Groeseneken, G.; Maes, H. E.; VanHoudt, J.; Witters, J. S. Basics of Nonvolatile Semiconductor Memory Devices. CiteSeerX 10.1.1.111.9431.

- ^ Bergemont, Albert; Chi, Min-Hwa (1997-05-05). "US Patent 5856222: Method of fabricating a high density EEPROM cell". patents.google.com. National Semiconductor Corp.

- ^ a b Skorobogatov, Sergei (2017). "How Microprobing Can Attack Encrypted Memory" (PDF). 2017 Euromicro Conference on Digital System Design (DSD). 2017 Euromicro Conference on Digital System Design (DSD). Vienna. pp. 244–251. doi:10.1109/DSD.2017.69. ISBN 978-1-5386-2146-2.

- ^ "Breaking copy protection in microcontrollers". www.cl.cam.ac.uk. Archived from the original on 2017-10-22.

- ^ "Frequently Asked Questions -ROHM Semiconductor". Archived from the original on 2011-02-19.

- ^ System Integration - From Transistor Design to Large Scale Integrated Circuits